### RFIC Design and Testing for Wireless Communications

A PragaTI (TI India Technical University) Course July 18, 21, 22, 2008

Lecture 8: Frequency synthesizer design I (PLL)

By

Vishwani D. Agrawal Fa Foster Dai

200 Broun Hall, Auburn University Auburn, AL 36849-5201, USA

### RFIC Design and Testing for Wireless Communications

#### **Topics**

#### Monday, July 21, 2008

| 9:00 – 10:30  | Introduction - Semiconductor history, RF characteristics |

|---------------|----------------------------------------------------------|

| 11:00 – 12:30 | Basic Concepts - Linearity, noise figure, dynamic range  |

| 2:00 - 3:30   | RF front-end design – LNA, mixer                         |

| 4:00 - 5:30   | Frequency synthesizer design I (PLL)                     |

#### **Tuesday, July 22, 2008**

| 9:00 - 10:30  | Frequency synthesizer design II   | (VCO)   |

|---------------|-----------------------------------|---------|

| 11:00 – 12:30 | RFIC design for wireless communic | cations |

| 2:00 - 3:30   | Analog and mixed signal testing   |         |

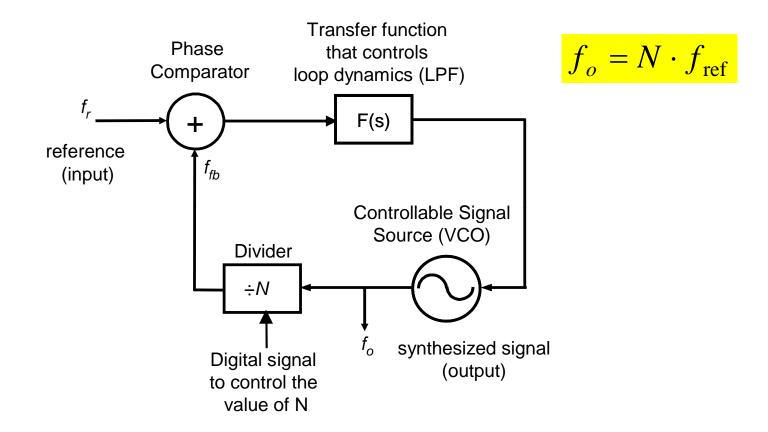

### Phase Lock Loop Integer-N Frequency Synthesizer

*N* is an integer  $\rightarrow$  the minimum step size =  $f_r \rightarrow$  to get a smaller step size, the reference frequency must be made smaller  $\rightarrow$  N must be higher in order to generate the same  $f_o \rightarrow$  larger phase noise (in-band noise magnified 20logN times by the loop).

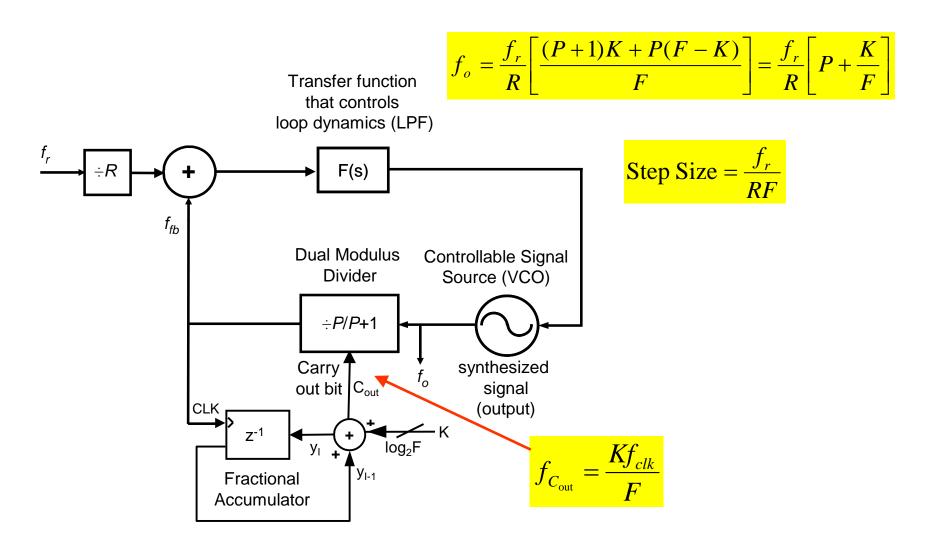

### **Fractional-N Concept**

If the loop divisor N is a fractional number, e.g., N=K/F, where K and F are integer numbers  $\rightarrow$  the minimum step size =  $f_r/F \rightarrow$  can achieve small step size without lowering the reference frequency  $\rightarrow$  loop divisor N can be small in order to generate the same  $f_o \rightarrow$  better phase noise (in-band noise magnified 20logN times by the loop).

How can we design a fractional divider? Divider is a digital block and its output transits only at the input clock edge → we can only generate integer frequency divider!!

Dual-modulus divider P/P+1: by toggling between the two integer division ratios, a fractional division ratio can be achieved by time-averaging the divider output. As an example, if the control changes the division ratio between 8 and 9, and the divider divides by 8 for 9 cycles and by 9 for 1 cycle and then the process repeats itself, then the average division ratio will be:

$$\overline{N} = \frac{8 \times 9 + 9 \times 1}{10} = 8.1$$

### Fractional-N synthesizer with a dual modulus prescaler

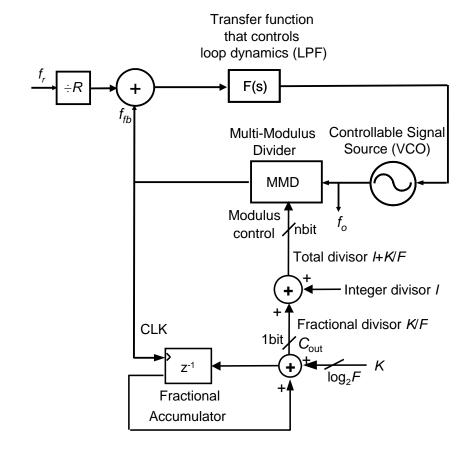

# Fractional-N frequency synthesizer with a multi-modulus divider

$$N_{\text{MMD}} = P_1 + 2^1 P_2 + \dots 2^{n-2} P_{n-1} + 2^{n-1} P_n + 2^n$$

$$f_o = \frac{f_r}{R} \left[ I + \frac{K}{F} \right]$$

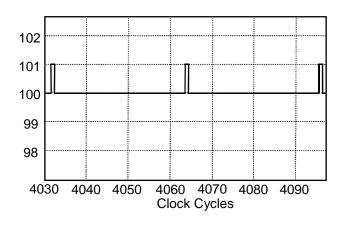

# Fractional-N Spurious Components

Any repeatable pattern in the time domain causes spurious tones in the frequency domain.

The fractional accumulator periodically generates the carry out that toggles the loop division ratio  $\rightarrow$  spurious tones at multiples of the carryout frequency  $f_r \cdot (K/F)$ , which is the step size of the fractional-N synthesizer.  $\rightarrow$  the smaller the step size is, the closer the spur locates to the carrier.

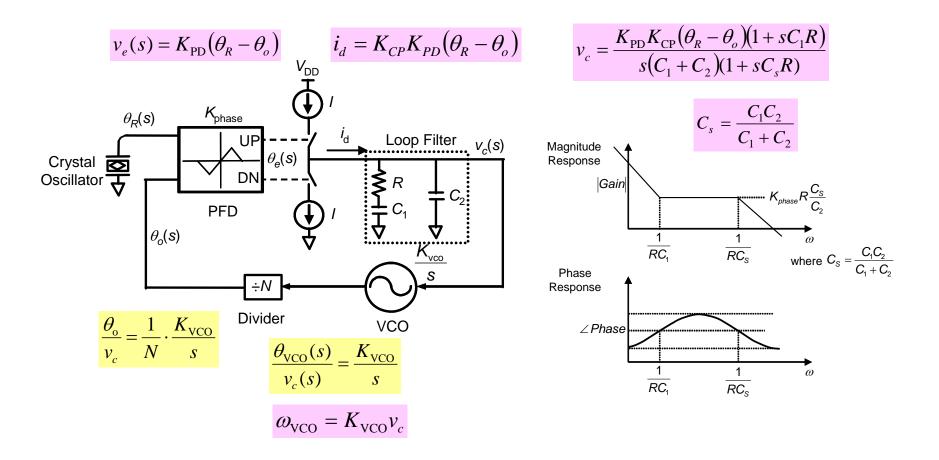

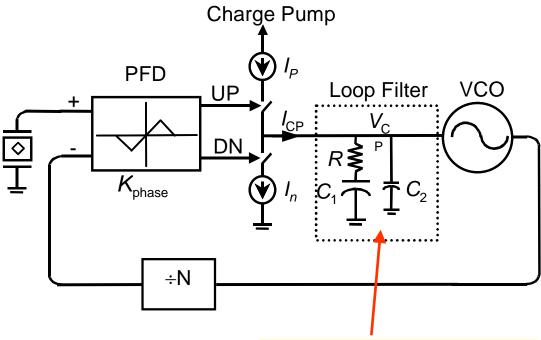

# **PLL Frequency Synthesizer**

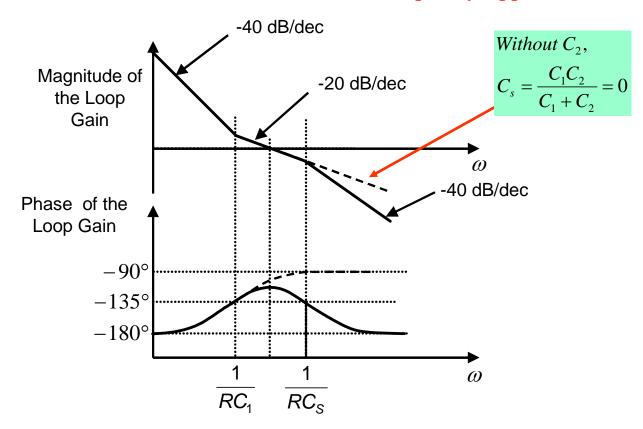

# **Open Loop Transfer Function**

$$\left(\frac{\theta_{o}}{\theta_{R}}\right)_{\text{open loop}} = \frac{K_{\text{VCO}}K_{\text{PD}}K_{\text{CP}}(1+sC_{1}R)}{s^{2}N(C_{1}+C_{2})(1+sC_{s}R)}$$

$C_2$  (about  $C_1/10$ ) adds a high frequency pole to clean up high frequency ripple on the control line.

# **Closed Loop Transfer Function**

$$\frac{\theta_{o}}{\theta_{R}} = \frac{K_{\text{VCO}}K_{\text{PD}}K_{\text{CP}}(1 + sC_{1}R)}{s^{2}N(C_{1} + C_{2})(1 + sC_{s}R) + K_{\text{VCO}}K_{\text{PD}}K_{\text{CP}}(1 + sC_{1}R)}$$

$$2nd - orderPLL$$

$$Without C_2, C_s = 0$$

$$\frac{2nd - orderPLL}{Without C_2, C_s = 0} \frac{\theta_o}{\theta_R} = \frac{K_{\text{VCO}} K_{\text{PD}} K_{\text{CP}} (1 + sC_1 R)}{s^2 N C_1 + K_{\text{VCO}} K_{\text{PD}} K_{\text{CP}} (1 + sC_1 R)}$$

natural frequency

$$\omega_n = \sqrt{\frac{K}{NC_1}}$$

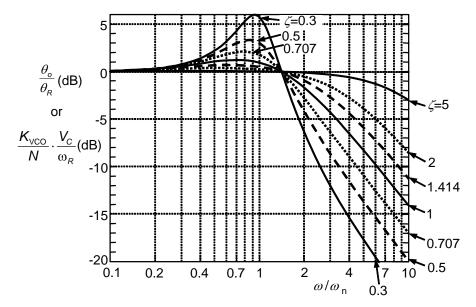

$\frac{\theta_o}{\theta_R} = \frac{\omega_n^2 \left(\frac{2\zeta}{\omega_n} s + 1\right)}{s^2 + 2\zeta\omega_n s + \omega_n^2}$   $\frac{\theta_o}{\theta_R} (dB)$  or  $\frac{\kappa_{\text{VCO}}}{N} \cdot \frac{V_c}{\omega_R} (dB)$  or  $\frac{\kappa_{\text{VCO}}}{N} \cdot \frac{V_c}{\omega_R} (dB)$  or  $\frac{\kappa_{\text{VCO}}}{N} \cdot \frac{V_c}{\omega_R} (dB)$

$$\zeta = \frac{R}{2} \sqrt{\frac{KC_1}{N}}$$

$$\omega_{3dB} = \omega_n \sqrt{1 + 2\zeta^2 + \sqrt{4\zeta^4 + 4\zeta^2 + 2}}$$

$$\omega_{3dB} \approx \left(1 + \zeta\sqrt{2}\right)\omega_n \quad \zeta < 1.5$$

$$\omega_{3dB} \approx 2\zeta\omega_n = K/N \qquad \zeta > 1.5$$

PLL frequency response

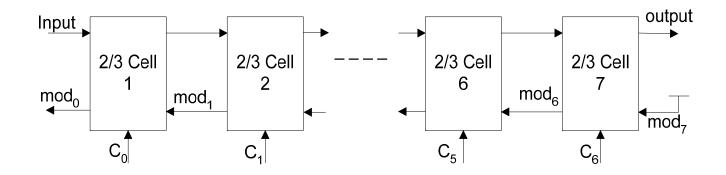

# MMD Architecture Using 2/3 Cells

$$N_{MMD} = 2^{n} + 2^{n-1}C_{n-1} + 2^{n-2}C_{n-2} + \dots + 2C_{1} + C_{0}$$

For 3 bit MMD,  $N_{MMD}(n = 3) = 8 + 4C_{2} + 2C_{1} + C_{0} = 8 \sim 15$

Say, we need an MMD with division ratios: 128-135.

$$N = 2^7 + 2^6 C_6 + 2^5 C_5 + 2^4 C_4 + 2^3 C_3 + 2^2 C_2 + 2^1 C_1 + C_0$$

The division ratios obtained using 2/3 cells: 128-255.

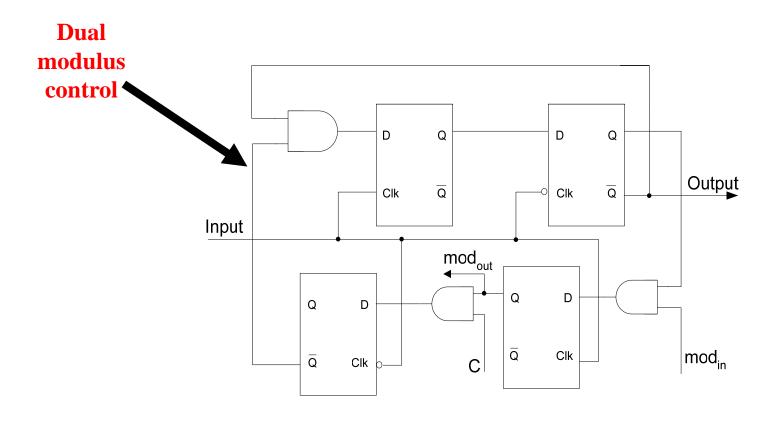

### **Dual Modulus Prescaler – 2/3 Cell**

mod<sub>in</sub>=1 and C=1  $\rightarrow$  F<sub>o</sub>/F<sub>in</sub>=1/3; mod<sub>in</sub>=1 and C=0  $\rightarrow$  F<sub>o</sub>/F<sub>in</sub>=1/2 mod<sub>in</sub>=0 and p=x  $\rightarrow$  F<sub>o</sub>/F<sub>in</sub>=1/2

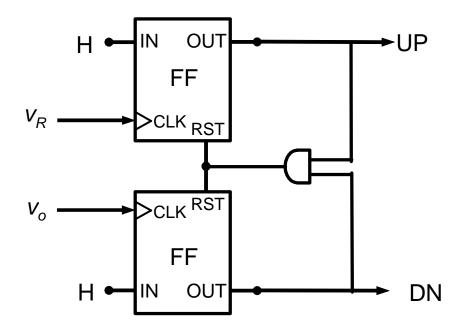

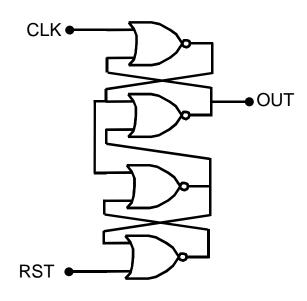

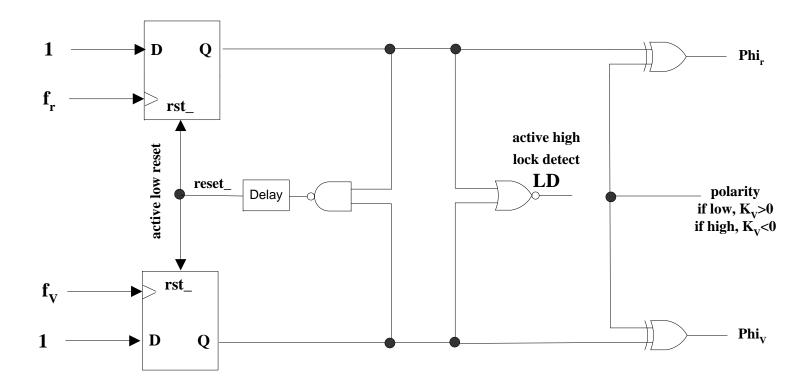

### **Tri-State PFD Circuit**

Positive edge-triggered D flip-flop with active low reset and hidden *D*=1

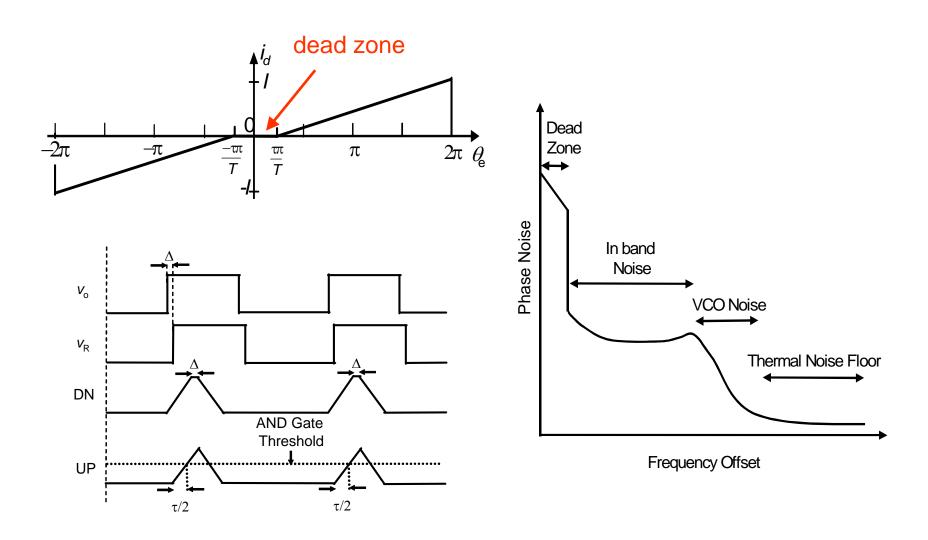

# **PFD Dead Zone**

### **Phase/Frequency Detector**

### **Tri-State Phase/Frequency Detector**

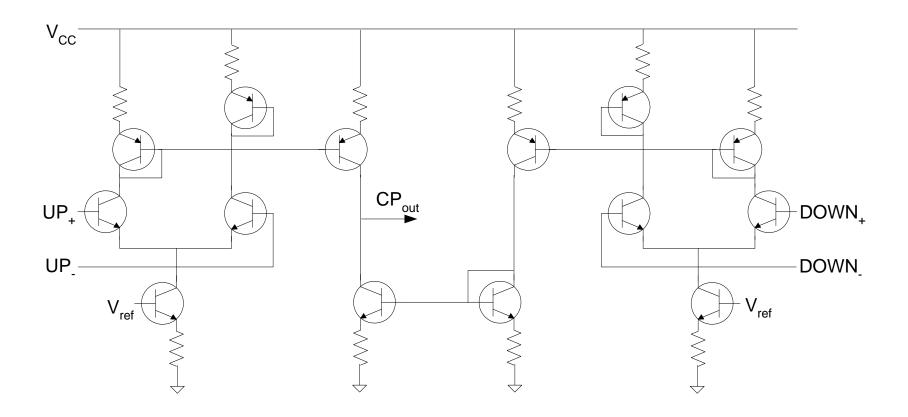

# Differential charge pump circuitry

# **2<sup>nd</sup> Order Passive Loop Filters**

The 2nd-order filter is the highest order passive RC filter that can be built without series resistors between the charge pump and the VCO tune line

$$F(s) = \frac{(1 + sC_1R)}{s(C_1 + C_2)(1 + sC_sR)}$$

$$C_s = \frac{C_1 C_2}{C_1 + C_2}$$

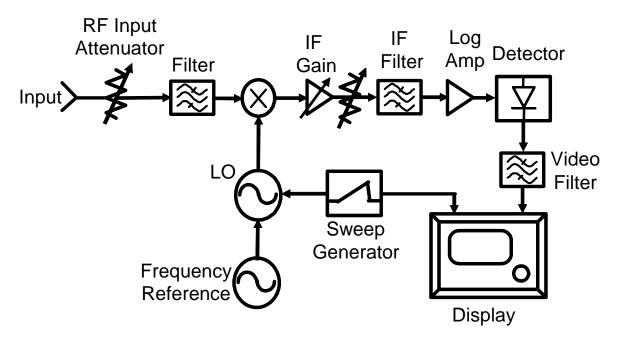

### Spectrum analyzer basic block diagram

#### Getting the Best Sensitivity Requires Three Settings

- Narrowest resolution bandwidth

- Minimum RF attenuation

- Sufficient video filter to smooth noise (VBW < 0.01 Resolution BW)</li>

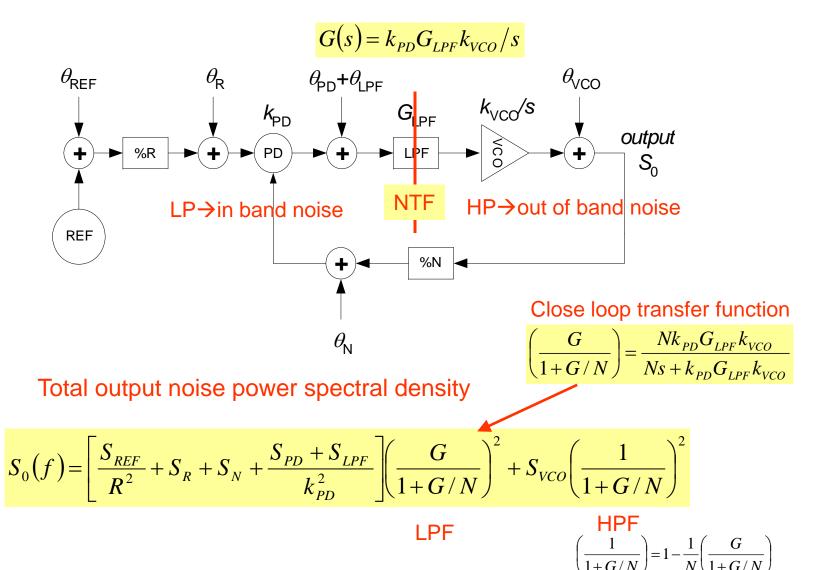

#### **PLL Phase Noise Sources**

#### **In-band PLL Phase Noise**

$$S_{0}(f) = \left[\frac{S_{REF}}{R^{2}} + S_{R} + S_{N} + \frac{S_{PD} + S_{LPF}}{k_{PD}^{2}}\right] \left(\frac{Nk_{PD}G_{LPF}k_{VCO}}{Ns + k_{PD}G_{LPF}k_{VCO}}\right)^{2} \xrightarrow{s \to 0} \left[\frac{S_{REF}}{R^{2}} + S_{R} + S_{N} + \frac{S_{PD} + S_{LPF}}{k_{PD}^{2}}\right] N^{2}$$

PLL magnifies the noise from the reference, phase detector, LPF and the dividers by the amount of 20logN dB → Smaller N leads to lower in-band noise.

For integer-N Synthesizer: output frequency Fo=Fref\*N, step size = Fref → cannot simultaneously achieve fine step size and small N. → poor in-band noise performance.

For fractional-N Synthesizer: output frequency Fo=Fref\*(N+K/F), step size = Fref/F → can achieve fine step size and small N simultaneously. → better inband noise performance.

#### **Out-Of-Band PLL Phase Noise**

The noise outside of the PLL bandwidth is determined by the VCO phase noise, namely,

$$S_0(f) = S_{VCO} \left( \frac{1}{1 + k_{PD} G_{LPF} k_{VCO} / Ns} \right)^2 \xrightarrow{s \to \infty} S_{VCO}$$

$$S_{VCO}(\Delta f) = 10\log\left\{\frac{FkT}{2P_s}\left[1 + \left(\frac{f_0}{2\Delta f \cdot Q_L}\right)^2\right] \cdot \left[1 + \frac{f_c}{|\Delta f|}\right]\right\}$$

Flicker 1/f noise is caused by trapping in the semiconductor material. Flicker noise corner fc is an empirical parameter depending on the device size and processing. For CMOS, fc is found to be  $3\sim7$  kHz typically and for bipolar transistors fc is about as 50 kHz. Notice that fc has impact only on close-in noise.  $Q_L$  is the loaded Q of the resonant circuit, ranging from  $5\sim20$  for on-chip resonator and  $40\sim80$  for off-chip tank. Ps is the average signal power at output of the oscillator active device, and F is oscillator effective noise factor.

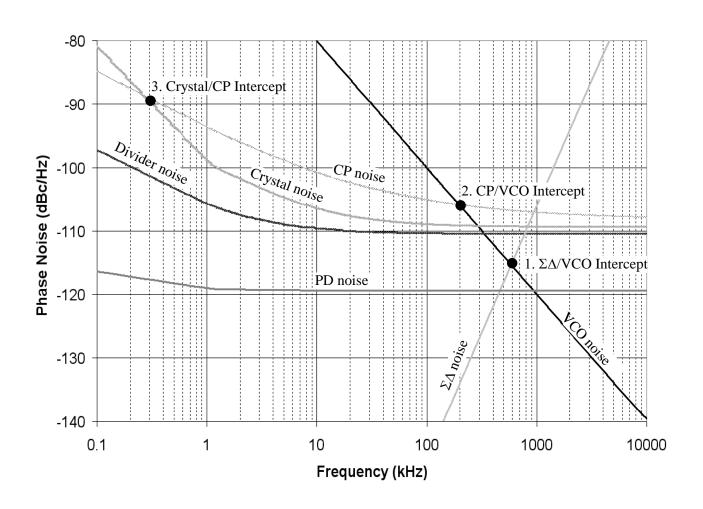

#### **Simulated PLL Phase Noise Sources**

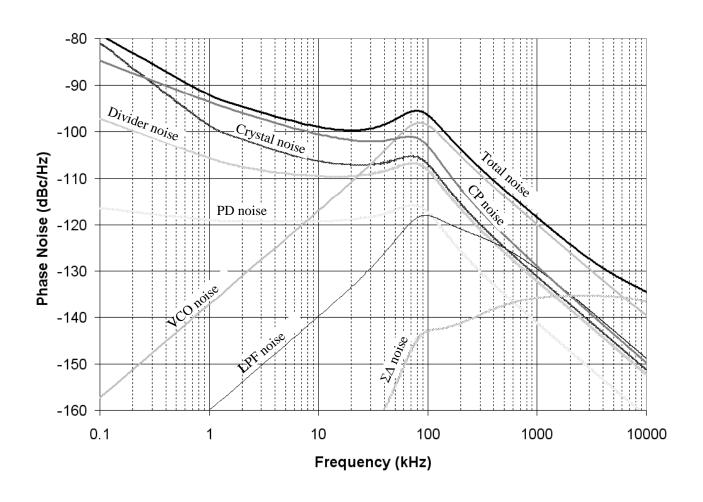

### **Simulated PLL Phase Noise With Loop Effect**

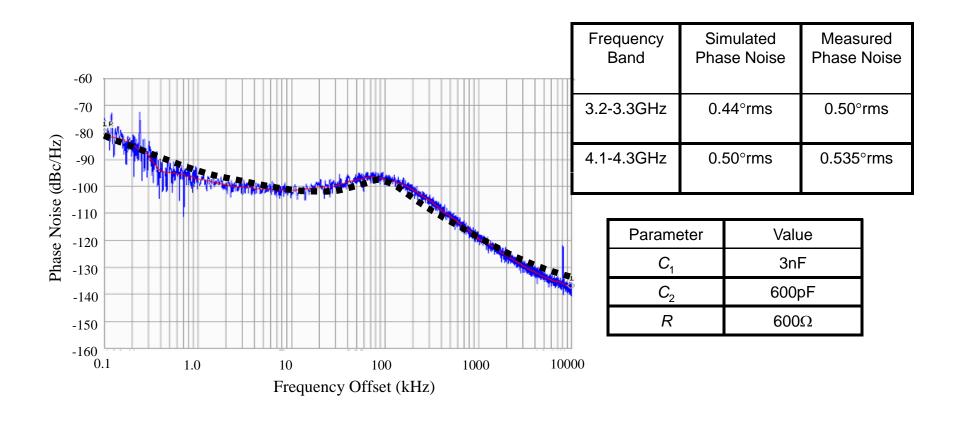

### Comparison of measured and simulated phase noise

#### References

- John W.M. Rogers, Calvin Plett, and Foster F. Dai, "Integrated Circuit Design for High-Speed Frequency Synthesis," ARTECH HOUSE PUBLISHERS, INC., ISBN: 1-58053-982-3, February, 2006.

- Fa Foster Dai and Charles Stroud, "Chapter 15 Analog and Mixed-Signal Test Architectures," in *System-on-Chip Test Architectures:* Nanometer Design for Testability, Morgan Kaufmann Publishers, ISBN: 978-0-12-373973-5, November 2007.

- John Rogers, Foster Dai and Calvin Plett, "Chapter 15 Frequency Synthesis for Multi-band Wireless Networks," in "Emerging Wireless Technologies -- From System to Transistors," CRC Press, ISBN: 978-0849379963, October 2007.

- RF Microelectronics by Behzad Razavi

- John W.M. Rogers, Foster F. Dai, Mark S. Cavin, and Dave G. Rahn, "A Fully Integrated Multi-Band SD Fractional-N Frequency Synthesizer for a MIMO WLAN Transceiver RFIC," *IEEE Journal of Solid-State Circuits*, vol. 40, no. 3, pp. 678-689, March, 2005.